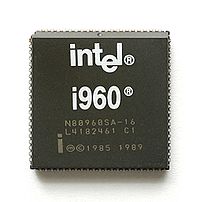

인텔 i960

인텔 i960 (80960)은 인텔의 RISC 마이크로프로세서이다. i960은 1990년대 임베디드 마이크로 컨트롤러로 경쟁하던 AMD 29000과 더불어 널리 사용되었다. 하지만 이러한 성공에도 불구하고 인텔은 DEC로부터 StrongARM의 생산 권리를 얻자 I960의 판매를 중지하였다.

개발

[편집]

1980년대 초반 인텔의 iAPX 432 실패로 말미암아 i960의 설계가 시작되었다. iAPX 432는 에이다(Ada), 리스프(Lisp)에서 지원하는 메모리 태그, 보호, 가비지 콜렉션(garbage collection) 등의 고급 언어를 하드웨어 상에서 직접 지원하려고 하였다. 그로 인해 명령어 집합은 복잡해졌고 멀티 칩으로 작동하였다. 또한 설계 결함으로 인해 당시의 다른 프로세서보다도 훨씬 느렸다.

1984년 인텔과 지멘스는 에이다를 사용한 고성능 오류 허용(fault-tolerant) 객체 지향의 컴퓨터 시스템을 개발하고자 BiiN이라는 공동 프로젝트를 시작했다. i432 개발팀원 대부분이 이 프로젝트에 합류하였지만 이들을 설계를 지휘한 사람은 IBM에서 온 글렌포드 마이어스(Glenford Myers)였다. BiiN 시스템은 은행이나 공장, 핵 발전소같은 높은 신뢰성을 필요로 하는 곳에 판매하고자 하였다.

i432의 보호된 메모리 개념은 BiiN 시스템의 새 프로세서를 설계하는데 큰 영향을 주었다. i432을 실패하게 만든 문제점을 피하고 성능을 증가시키기 위해 다수의 기능이 추가되었으며 그 결과 i960이 설계되었다. 1985년 10월 테이핑 아웃(taping out)이라 불리는 칩 설계의 마지막 단계로 들어가 제조 공장으로 보내졌으며 그 후 몇 달 뒤에 동작되는 최초의 960을 만들어냈다.

BiiN은 지멘스의 조직 개편으로 인해 중지되었고 960MX는 사용되지 않은 채 남겨졌다. 마이어스는 완전한 기능의 BiiN에서 몇 가지 기능 축소판(subsets)을 구상해 범용 프로세서로서 i960의 판매를 인텔 경영진에게 설득하기 시작하였으며 인텔 80286과 386(i960 처음 생산된 달 테이핑 아웃되었다.)을 대체하는 용도와 스티브 잡스의 넥스트(NeXT)를 포함한 유닉스 시스템용 신규 RISC 시장에서의 사용을 타진하였다. 당시 i960은 인텔 내부에서 386 진영뿐 아니라 또 다른 RISC 프로세서 i860과도 경쟁해야 했다. 마이어스는 인텔 경영진을 설득하지 못했고 i960의 유닉스 프로세서 또는 범용 판매에 대한 지원을 받지 못했다. 하지만 곧 고성능 32비트 임베디드라는 새로운 시장을 발견하게 된다.

아키텍처

[편집]i432를 괴롭히던 낮은 성능 문제를 피하기 위해 i960의 명령어 집합은 RISC를 기반으로 하고 있다. 메모리 시스템은 32비트 워드와 메모리 보호를 위한 태그 비트로 이루어진 33비트 넓이로 되어 있다. 레지스터 윈도를 적용하는 등, 많은 면에서 i960은 오리지널 버클리 RISC의 설계를 따르고 있다. 버클리 RISC 경쟁자인 스탠포드 대학의 디자인(MIPS)은 컴파일러가 최적화된 코드를 생산하는 것에 의존하는데 i960에 이것을 적용하지 않았다. I386과는 다르게 메모리 세그먼트 없이 완전한 32비트 메모리 공간을 사용할 수 있다. i960은 슈퍼스칼라(superscalar)를 적용해 명령어는 프로세서 내부에서 1개 이상의 유닛으로 동시에 디스패치(dispatch)된다.

i960 버전

[편집]완전한 기능을 가진 i960MX는 군용으로만 납품되었지만 또 다른 i960MC은 고성능 임베디드용으로 판매되었다. i960MC은 오리지널 BiiN의 모든 기능을 가지고 있지만 이 기능들은 문서로 기재되어 있지 않으며 많은 수의 핀도 사용되지 않는다.

80960Kx

[편집]i960KA는 메모리 관리 장치(MMC)와 FPU가 없는 제품이며 i960KB는 FPU를 내장하고 있다. 두 버전은 내부적으로 동일하며 제품 라벨만 다르다. i960KA는 레이저 프린터용의 저가형 32비트 프로세서로 널리 사용되었을 뿐만 아니라 초기 그래픽 단말기와 기타 임베디드 응용에도 사용되었다.

80960Cx

[편집]i960CA는 완전한 RISC 실행이 적용된 첫 프로세서로 1989년 7월에 발표되었다. 새로 설계된 슈퍼스칼라 RISC 코어와 주소 지정이 가능한(addressable) 온 칩 캐시가 추가되었다. 하지만 고성능 임베디드 용도로 FPU와 MMC가 제외되었다. i960CA는 슈퍼스칼라 실행이 가능한 첫 번째 싱글 칩이었다. C 시리즈는 ALU를 하나만 가지고 있었지만 산술 명령어, 메모리 참조, 분기 명령어를 동시에 디스패치, 실행할 수 있었다. 첫 번째 i960CA는 33 MHz으로 동작했으며 인텔은 66 MIPS의 성능을 광고했다. 나중에 FPU가 포함되고 MMU는 제외된 i960CF도 판매되었다.

80960Jx

[편집]80960Jx는 임베디드용 프로세서로 32비트 데이터/어드레스 복합(multiplex) 버스, 명령어와 데이터 캐시, 1K 온 칩 램, 인터럽트 컨트롤러와 2개의 독립된 32비트 타이머를 내장했다. 80960Jx의 검사 기능으로 ONCE(on-circuit emulation) 모드와 JTAG(boundary scan)이 가지고 있다.

80960VH

[편집]1998년 10월 발표된 i960VH 임베디드 PCI 프로세서는 100MHz i960JT 코어와 33MHz 32비트 PCI 버스, 16KB 명령어 캐시, 4KB 데이터 캐시, 1KB 내장 램, 2개의 32비트 타이머, 프로그래머블 인터럽트 컨트롤러, I²C 인터페이스, 2채널 DMA 컨트롤러를 갖추고 있다.

종료

[편집]인텔은 I2O(Intelligent Input/Output)를 내세워 I/O 디바이스 컨트롤러 시장에서 i960의 입지를 강화하였지만 개량 작업은 끝났다. 1990년 중반 다른 신쳥 칩셋에 비해 i960의 가격대 성능비가 떨어졌고 배터리 전원을 사용하는 시스템을 위한 저전력 버전도 출시하지 않았다. 1990년 i960 개발팀은 P6 프로세서 개발에 배치되어 나중에 펜티엄 프로를 발표한다.

현재

[편집]i960 프로세서는 XOR 연산 성능이 높아서 고성능 레이드(RAID) 컨트롤러 카드에 사용되기도 한다. i960RS가 사용된 아답텍 AAR-2400A는 소규모 PC 서버와 워크스테이션 용도로 RAID-5와 병렬 ATA 하드 디스크 4개를 사용할 수 있다.

인텔 960은 브로케이드(Brocade)의 파이버 채널 스위치에 사용되어 Fabric OS를 작동시킨다.

인텔 960은 슬롯 머신에도 사용되었는데 IGT의 스텝퍼 S2000 계열, i960 비디오 계열에서 찾아볼 수 있다.

미국이 개발한 스텔스 전투기 F-22의 CIP에 주요 프로세서로 사용되었다.

한국이 개발한 훈련기 KA-1의 컴퓨터에 주요 프로세서로 사용되었다.

인도가 개발한 경전투기 HAL 테자스(Tejas)의 MMR(Multi-mode radar)에도 i960이 사용되었다고 한다. HAL 테자스는 2010경 인도 공군에 배치될 예정이다.

인텔 960은 켈빈 휴즈(Kelvin Hughes)의 자동 레이다 기록 장치(ARPA : Automatic Radar Plotting Aid)의 인터페이스에도 사용되었다.

인텔 960은 HP의 X-Terminals에도 사용되었다.

사타 레이드 컨트롤러로 사용되는 인텔 80303 IOP (Intellegent I/O Processor)은 80960JT-100 코어와 메모리 컨트롤러, PCI-to-PCI 브리지를 내장하고 있다.